200GにおけるElectricalインターフェ...

02

05

200GにおけるElectricalインターフェースを検討、通信に必要な消費電力は半減へ

200Gが通ることを前提に、Electricalインターフェース側を検討

前々回、前回は、主にOptical周りの話に終始したわけだが、Electricalインターフェース側の検討も行われた。

これは単純な話で、100G×8であれば送受信は8レーンずつだから、これは「QSFP-DD」(というかこちらで紹介した「QSFP-DD800」)、あるいはこちらで紹介した「OSFP」で対応ができる。

これは、光インターフェース側が100G×8ではなく200G×4になった場合も同じだ。2:1 Gearboxを入れれば、モジュール内部で200G×4へと変換できる(まだ実現可能性の検討の段階なので、実装時の消費電力やコストは考慮外)から、そう難しくはない。

問題はその先、1.6Tを狙う場合だ。200G×8が必須となる構成で、Electricalインターフェースの側を100G×16というのは、さすがにあり得ない。

そもそもそんなモジュール規格は存在しないし、開発してもCFP2/CFP8並の大きさになることは必須で、下手をすると以下のようにCFP並みの大きさになりかねず、当然現在のQSFP/OSFP系モジュールとの互換性もなくなる。QSFP/OSFP系の信号端子を片方向16レーンずつに拡充するのも困難だろう。

CFP MSAのウェブページに示されているモジュールの寸法図。ちなみにこの高さはヒートシンクを付けない場合で、ヒートシンクを付ければ倍増するついでに言えば、100G×8が容易なわけでもない。QSFP-DD800では2段積みモジュールの場合、上段では直接信号を引っ張り出すなんてトリッキーな規格が標準化されたのは、それだけ取り回しが困難なことの裏返しである。

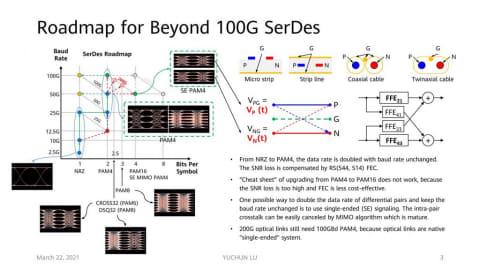

QSFP-DD800の2段積みモジュールの分解図。下側のコネクタはともかく、上側の配線は凄いことに。出典はQSFP-DD800 Specification Rev 1.0のFigure 3-5話を戻すと、そんなわけでレーンあたり200GのElectrical Signalingについての検討も行われた。"Considerations on 200G per lane PAM Signaling"というプレゼンテーションがHuaweiのYuchun Lu氏およびYan Zhuang氏から発表されている。

その前提条件として、200G(正確には212.5Gbps)の信号を通すことが大前提にある。

"Compatible with 100G and slower speed link"以外は、全て敷居が高そうな課題ばかりだちなみに、冒頭で説明した話は、モジュールのインターフェース(AUI)を念頭に置いたものだが、実際にはモジュール内部のLSIにおけるダイ同士の接続や、モジュール内部の配線なども視野に入っている。逆に、KRとかCRといったBackplane/Copper Interconnect系は、ここでは考慮の対象外である(とは言え、Power Efficiencyのところには、KR/CRがちゃっかり入っているのが怖い)。

おそらくKR/CRに関しては、同じ規格では距離が長すぎて、そのままでは到達が難しいため、追加のFECなどを入れないと実現はできないと思われるが、そもそも配線が1フィート未満の規格が実現できなければ1mオーダーの規格が成立しないのは自明で、KR/CRの規格の基礎として、まずは1ft未満というかcmオーダーの配線規格を策定したい、ということだろう。